I-D-FET iku-0 esangweni bias xa kukho itshaneli, inokuqhuba iFET; I-E-FET iku-0 esangweni bias xa kungekho tshaneli, ayikwazi ukuqhuba iFET. ezi ndidi zimbini zeeFET zineempawu zazo kunye nokusetyenziswa kwazo. Ngokubanzi, uphuculo lwe-FET kwiisekethe ezinesantya esiphezulu, ezinamandla aphantsi zixabiseke kakhulu; kwaye esi sixhobo siyasebenza, yi-polarity yesango bias voi-litage kunye ne-drain I-voltage efanayo, ilungele ngakumbi kuyilo lwesekethe.

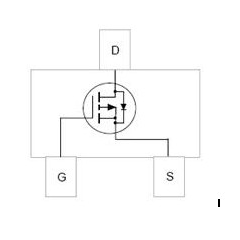

Into ebizwa ngokuba yinkqubo yokuphucula: xa i-VGS = i-0 ityhubhu yimeko yokunqunyulwa, kunye ne-VGS echanekileyo, uninzi lwabathwali bakhangwa esangweni, ngaloo ndlela "ukuphucula" abathwali kwingingqi, benza umgudu wokuqhuba. I-n-channel eyomeleziweyo ye-MOSFET sisiseko se-symmetrical topology yasekhohlo-ekunene, eyi-P-type semiconductor ekuveliseni umaleko we-SiO2 yokugquma ifilimu. Ivelisa umaleko okhuselayo wefilimu ye-SiO2 kwi-P-type semiconductor, kwaye emva koko isasaze imimandla emibini enodidi oluphezulu lwe-Nifotolithography, kwaye ikhokelela i-electrodes ukusuka kummandla we-N-uhlobo, enye ye-drain D kunye nenye yomthombo S. Uluhlu lwensimbi ye-aluminium lufakwe kwi-insulating layer phakathi komthombo kunye ne-drain njengesango G. Xa VGS = 0 V , kukho iidiode ezimbalwa ezine-back-to-back diodes phakathi kombhobho kunye nomthombo kwaye amandla ombane phakathi kwe-D kunye ne-S ayenzi i-current phakathi kwe-D kunye ne-S. Umbane phakathi kwe-D kunye ne-S ayenziwanga ngumbane osetyenziswayo .

Xa i-voltage yesango yongezwa, ukuba i-0 < VGS < VGS (th), ngokusebenzisa intsimi yombane ene-capacitive eyenziwe phakathi kwesango kunye ne-substrate, imingxuma ye-polyon kwi-semiconductor yohlobo lwe-P kufuphi nomzantsi wesango igxothwa phantsi, kwaye umaleko obhityileyo wokuncipha kweeyoni ezingalunganga ubonakala; kwangaxeshanye, iya kutsala oligons kuyo ukuba bafudukele kumphezulu umaleko, kodwa inani lilinganiselwe kwaye akwanelanga ukwenza umjelo conductive enxibelelana idreyini kunye nomthombo, ngoko ke akwanelanga Formation of idreyini ID yangoku. ukwanda ngakumbi VGS, xa VGS > I-VGS (th) (VGS (th) ibizwa ngokuba yi-voltage yokuvula), kuba ngeli xesha amandla ombane esango aye aqina kakhulu, kuluhlu lwe-P-uhlobo lwe-semiconductor umphezulu kufuphi nomzantsi wesango ngaphantsi kokuhlanganiswa kwezinto ezininzi. ii-electron, unokwenza umsele, umsele kunye nomthombo wonxibelelwano. Ukuba i-voltage ye-drain source yongezwa ngeli xesha, i-drain current ingenziwa i-ID. ii-electron kwijelo conductive eyenziwe ngaphantsi kwesango, ngenxa umngxuma carrier kunye P-uhlobo semiconductor polarity ichasene, ngoko ibizwa ngokuba anti-uhlobo umaleko. Njengoko i-VGS iqhubeka nokukhula, i-ID iya kuqhubeka ikhula. I-ID = 0 kwi-VGS = 0V, kwaye i-drain current iyenzeka kuphela emva kwe-VGS> VGS(th), ngoko ke, olu hlobo lwe-MOSFET lubizwa ngokuba yi-smedyment MOSFET.

Ubudlelwane bolawulo lwe-VGS kwi-drain current inokuchazwa yi-curve iD = f(VGS(th))|VDS=const, ebizwa ngokuba yi-curve characteristic curve, kunye nobukhulu beslope se-curve yeempawu zodluliselo, gm, ibonakalisa ulawulo lokuphuma kwamanzi ngesango lombane lomthombo. ubukhulu be-gm yi-mA/V, ngoko ke i-gm ikwabizwa ngokuba yi-transconductance.